# INTERACTIVE HIGH PERFORMANCE VOLUME RENDERING

Inaugural-Dissertation zur Erlangung des Doktorgrades der Mathematisch-Naturwissenschaftlichen Fakultät der Universität zu Köln

vorgelegt von

### STEFAN ZELLMANN

aus Bergisch Gladbach

Hundt Druck GmbH, Köln Jahr der Veröffentlichung: 2014 Berichterstatter/in: Prof. Dr.-Ing. Ulrich Lang Prof. Dr. Ewald Speckenmeyer

Tag der mündlichen Prüfung: 7. Juli 2014

© Copyright by Stefan Zellmann 2014 All Rights Reserved

# Abstract

This thesis is about Direct Volume Rendering on high performance computing systems. As direct rendering methods do not create a lower-dimensional geometric representation, the whole scientific dataset must be kept in memory. Thus, this family of algorithms has a tremendous resource demand. Direct Volume Rendering algorithms in general are well suited to be implemented for dedicated graphics hardware. Nevertheless, high performance computing systems often do not provide resources for hardware accelerated rendering, so that the visualization algorithm must be implemented for the available general-purpose hardware.

Ever growing datasets that imply copying large amounts of data from the compute system to the workstation of the scientist, and the need to review intermediate simulation results, make porting Direct Volume Rendering to high performance computing systems highly relevant. The contribution of this thesis is twofold.

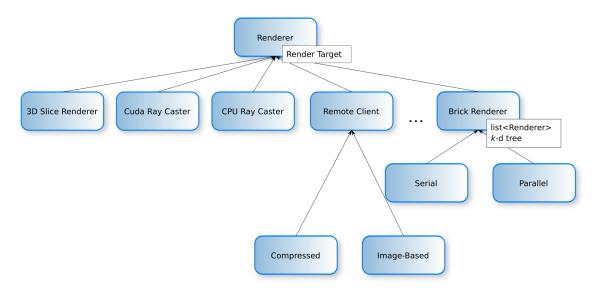

As part of the first contribution, after devising a software architecture for general implementations of Direct Volume Rendering on highly parallel platforms, parallelization issues and implementation details for various modern architectures are discussed. The contribution results in a highly parallel implementation that tackles several platforms.

The second contribution is concerned with the display phase of the "Distributed Volume Rendering Pipeline". Rendering on a high performance computing system typically implies displaying the rendered result at a remote location. This thesis presents a remote rendering technique that is capable of hiding latency and can thus be used in an interactive environment.

# Kurzfassung

Diese Dissertation fokussiert sich auf direktes Volume Rendering auf Höchstleistungsrechnern. Weil für direkte Visualierungsmethoden keine geometrische Hilfsrepräsentation niedrigerer Dimension benötigt wird, so dass der gesamte wissenschaftliche Datensatz im Arbeitsspeicher vorgehalten werden muss, ist der Ressourcenbedarf dieser Familie von Algorithmen immens. Im Allgemeinen bietet sich zur Implementierung eher Grafikhardware an. Diese wird von Höchstleistungsrechnern häufig aber nicht zur Verfügung gestellt, so dass der Visualisierungsalgorithmus speziell für die verfügbare, für den universellen Einsatz gedachte, Hardware implementiert werden muss.

Das stete Wachstum wissenschaftlicher Datensätze impliziert Datenbewegungen im großen Maße vom Höchstleistungsrechner zur Workstation des Wissenschaftlers. Außerdem besteht zunehmend der Bedarf danach, Zwischenergebnisse bereits während der Simulation begutachten zu können. Diese zwei Faktoren begründen die Relevanz dessen, Direktes Volume Rendering für Höchstleistungsrechner zu portieren. Der Beitrag dieser Arbeit ist zu diesem Zwecke zweigeteilt.

Im Rahmen des ersten Teilbeitrags werden auf der Basis einer Software-Architekturbeschreibung, die generelle Implementierungen von Direktem Volume Rendering für hochgradig parallele Plattformen lanciert, Details zur parallelen Implementierung für zahlreiche moderne Architekturen erörtert. Dieser Teilbeitrag resultiert in einer hochgradig parallelen Implementierung, die auf zahlreichen Plattformen effizient lauffähig ist.

Der zweite Teilbeitrag behandelt die Darstellungsphase in der "Verteilten Volume Rendering Pipeline". Rendering auf Höchstleistungsrechnern basiert typischerweise auf Remote Rendering Techniken. Diese Dissertation schlägt eine Remote Rendering Technik vor, mit deren Hilfe es möglich ist, Latenzen zu verstecken, und die deshalb in interaktiven Umgebungen zum Einsatz kommen kann.

# Acknowledgements

First and foremost I would like to thank my advisor Prof. Dr. Ulrich Lang. He gave me the opportunity to study an interesting topic in depth. I consider it a privilege. Furthermore, I would like to thank Dr. Jürgen Schulze and the scientists at the High Performance Computing Center Stuttgart (HLRS), who initially developed the DeskVOX volume rendering software. Without their groundwork, this thesis would not have been possible at all.

Special thanks go to my former colleague Martin Aumüller who has been a guide, especially in my first years as a scientist.

My thanks go also to my two student coworkers, Alexander Bolz and Stavros Delisavas. Programming is primarily a lot of work, and much of the work conducted during the course of this thesis would have been left undone without their help.

I also wish to thank my colleagues who read this thesis and who influenced me with their interesting discussions. Their suggestions contributed to the quality of this work. My thanks go, in alphabetical order, to Viktor Achter, Matthias Flasko, and Yvonne Percan.

Some of the figures and results in this thesis are reprints and were originally published by ASME and IASTED, respectively. The original publications are acknowledged at the positions where they occur in the text. The figures were reprinted with friendly permission of the respective copyright owner.

The work for this thesis was conducted over a period of almost five years. During that time, my work was supported by the German Federal Ministry of Education and Research (BMBF), who funded the research project "Visualization in Parallel Manycore Environments" (VisPME) [Vis11]. Later, my work was supported by a grant from the Centre for High-Performance Scientific Computing in Terrestrial Systems, HPSC TerrSys, in the Geoverbund ABC/J [HPS12].

# Contents

| 1 Introduction |      |                                                                                                                                                            |   |  |

|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|

|                | 1.1  | Structure                                                                                                                                                  | 1 |  |

|                | 1.2  | Motivation                                                                                                                                                 | 3 |  |

|                | 1.3  | Contributions                                                                                                                                              | 4 |  |

| <b>2</b>       | Scie | ntific Visualization                                                                                                                                       | 5 |  |

|                | 2.1  | Brief Introduction to Scientific Visualization                                                                                                             | 6 |  |

|                | 2.2  | Classification of Scientific Datasets                                                                                                                      | 8 |  |

|                | 2.3  | Visualization Pipelines                                                                                                                                    | 1 |  |

|                | 2.4  | Visualization Methods for Scientific Datasets                                                                                                              |   |  |

|                |      | 2.4.1 Contouring $\ldots \ldots \ldots$    | 3 |  |

|                |      | 2.4.2 Slicing                                                                                                                                              | 5 |  |

|                |      | 2.4.3 Particle Tracing                                                                                                                                     | 5 |  |

|                |      | 2.4.4 Color Mapping $\ldots \ldots \ldots$ | 6 |  |

|                | 2.5  | Scientific Visualization and High Performance Computing 1                                                                                                  | 8 |  |

|                |      |                                                                                                                                                            |   |  |

### 3 State of the Art in Parallel Direct Volume Rendering 19

| 3.1 | Introd  | uction to Direct Volume Rendering                                                                           | 20 |

|-----|---------|-------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Direct  | Volume Rendering Algorithms                                                                                 | 29 |

|     | 3.2.1   | Texture-Based Volume Rendering                                                                              | 30 |

|     | 3.2.2   | Frequency Domain Volume Rendering                                                                           | 33 |

|     | 3.2.3   | Shear-Warp Volume Rendering                                                                                 | 34 |

|     | 3.2.4   | Volume Splatting                                                                                            | 35 |

|     | 3.2.5   | Cell Projection                                                                                             | 39 |

|     | 3.2.6   | Ray Casting                                                                                                 | 41 |

|     | 3.2.7   | Out-of-Core Volume Rendering                                                                                | 42 |

| 3.3 | Paralle | el Programming Models                                                                                       | 43 |

|     | 3.3.1   | Single Instruction Multiple Data                                                                            | 46 |

|     | 3.3.2   | Shared Memory Computing                                                                                     | 47 |

|     | 3.3.3   | Distributed Memory Computing                                                                                | 49 |

|     | 3.3.4   | General-Purpose Programming with $\operatorname{NVIDIA}^{\textcircled{R}}$ GPGPUs                           | 50 |

|     | 3.3.5   | Programming Models for the $\mathrm{Intel}^{\textcircled{R}}$ Xeon $\mathrm{Phi}^{\mathrm{TM}}$ Coprocessor | 53 |

| 3.4 | Paralle | el Direct Volume Rendering Techniques                                                                       | 55 |

|     | 3.4.1   | Sorting Classification for Parallel Rendering                                                               | 55 |

|     | 3.4.2   | Sort-First Volume Ray Casting                                                                               | 57 |

|     | 3.4.3   | Sort-Last Parallelization for Multi-GPU Systems and Dis-<br>tributed Memory Systems                         | 59 |

|     | 3.4.4   | Load-Balancing for Parallel Direct Volume Rendering                                                         | 63 |

| 3.5 | Direct  | Volume Rendering and Visualization Systems                                                                  | 65 |

|     | 3.5.1   | ImageVis3D                                                                                                  | 65 |

|   |     | 3.5.2                                                                     | Voreen                                                                       | 65 |

|---|-----|---------------------------------------------------------------------------|------------------------------------------------------------------------------|----|

|   |     | 3.5.3                                                                     | DeskVOX                                                                      | 66 |

|   |     | 3.5.4                                                                     | ParaView                                                                     | 67 |

|   |     | 3.5.5                                                                     | VisIt                                                                        | 67 |

|   |     | 3.5.6                                                                     | COVISE                                                                       | 68 |

| 4 | A S | oftwar                                                                    | e Architecture for Distributed Volume Rendering                              | 69 |

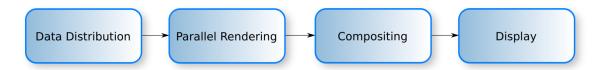

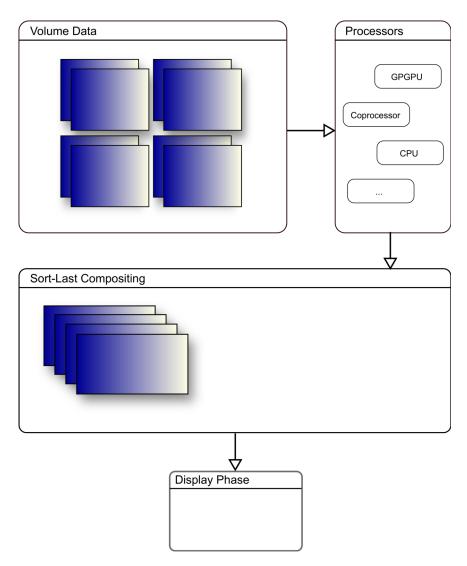

|   | 4.1 | Distril                                                                   | buted Volume Rendering                                                       | 70 |

|   | 4.2 | The D                                                                     | istributed Volume Rendering Pipeline                                         | 71 |

|   | 4.3 | Data l                                                                    | Distribution                                                                 | 72 |

|   | 4.4 | Gener                                                                     | ic Parallelization Scheme for Sort-Last Rendering                            | 73 |

|   | 4.5 | Displa                                                                    | y Phase                                                                      | 75 |

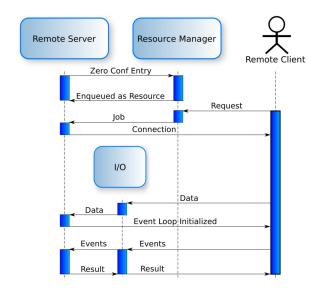

|   | 4.6 | Intera                                                                    | ctive Resource Management                                                    | 76 |

|   |     | 4.6.1                                                                     | One Resource Per User                                                        | 76 |

|   |     | 4.6.2                                                                     | Multiple Resources Per User                                                  | 77 |

| 5 | -   |                                                                           | ting the Parallel Rendering Phase of the Distributed Vol-<br>lering Pipeline | 79 |

|   | 5.1 | Sort-First Volume Ray Casting for High<br>Performance Computing Platforms |                                                                              |    |

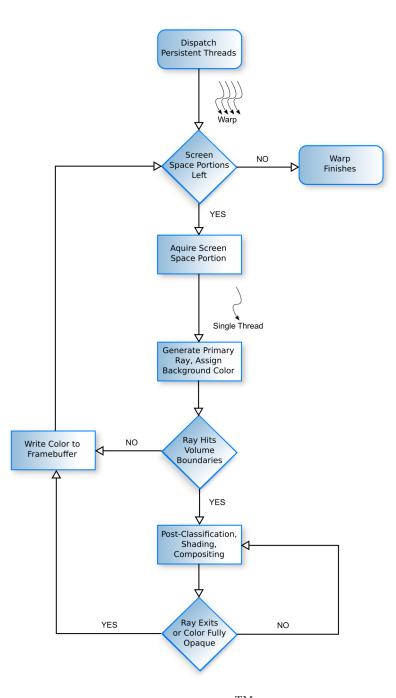

|   |     | 5.1.1                                                                     | GPGPU Volume Ray Casting Implementation                                      | 81 |

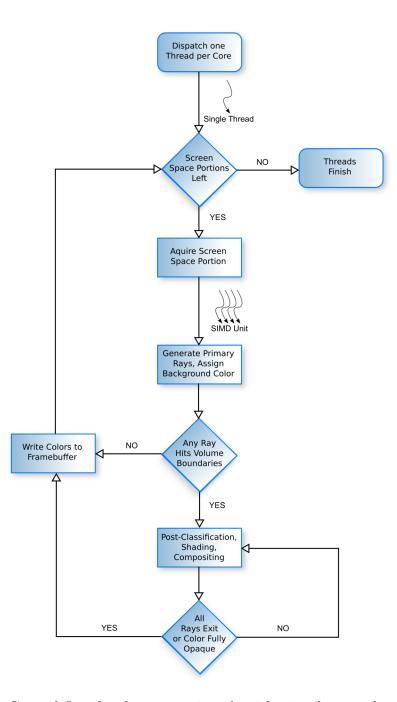

|   |     | 5.1.2                                                                     | Sort-First Parallel Volume Ray Casting for Multi-Core Systems                | 86 |

|   |     | 5.1.3                                                                     | SIMD-Based Ray Casting Kernel for Intel <sup>®</sup> -<br>Compatible CPUs    | 89 |

| tions 103 |

|-----------|

| 105       |

| 106       |

| 108       |

| 122       |

| 125       |

| 126       |

| 129       |

| y129      |

| 131       |

| 134       |

| 137       |

| 140       |

| 141       |

| 141       |

| 144       |

| 145       |

| 146       |

| 148       |

| 148       |

| 156       |

| •         |

#### CONTENTS

|    | 6.6    | Conclusions                              | 163 |  |  |

|----|--------|------------------------------------------|-----|--|--|

| 7  | Sun    | nmary, Conclusions and Future Work       | 165 |  |  |

|    | 7.1    | Contributions and Relevance of this Work | 165 |  |  |

|    | 7.2    | Conclusions                              | 167 |  |  |

|    | 7.3    | Outlook                                  | 168 |  |  |

| Bi | ibliog | graphy                                   | 171 |  |  |

#### CONTENTS

### Chapter 1

## Introduction

### 1.1 Structure

This thesis is structured as follows.

**Chapter 1**, i. e. the remainder of this chapter, outlines the motivation for this thesis. This is followed by a brief overview of the two main contributions presented in this work.

**Chapter 2** gives a general overview of scientific visualization algorithms. Being far from comprehensive, this chapter classifies the scientific visualization algorithms that later on are investigated more thoroughly in a broader context.

**Chapter 3** summarizes the current state of the art for parallel Direct Volume Rendering algorithms. The problem setting for Direct Volume Rendering along with algorithms to achieve it in real-time is presented. Along with that, parallelization strategies are reviewed that are suitable for different kinds of hardware that is typically found in high performance computing systems.

**Chapter 4** devises a software architecture for Distributed Volume Rendering on high performance computing systems. The software architecture follows a pipeline approach. With maximum versatility in mind, the chapter outlines how specialization of various pipeline stages can lead to a visualization tool that is capable of running on highly heterogeneous hardware platforms with manifold usage scenarios ranging from interactive applications in Virtual Reality over in situ visualization to visualization of large datasets on dedicated graphics hardware.

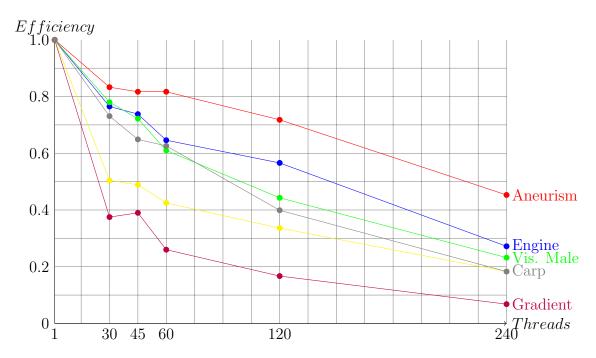

**Chapter 5** is concerned with the first major contribution of this thesis and proposes a concrete implementation of the parallel rendering stage of the Distributed Volume Rendering Pipeline introduced in Chapter 4. A sort-last Multi-GPU implementation is accompanied by a CPU-based SIMD implementation, that scales to modern hardware platforms like the Intel<sup>®</sup> Xeon Phi<sup>TM</sup> coprocessor. The rendering performance of the system is evaluated.

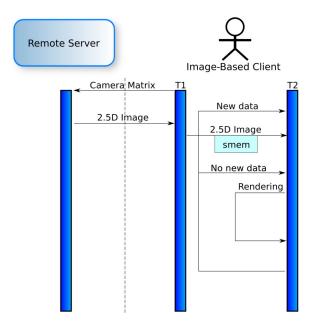

**Chapter 6** elaborates on the second contribution of this work and devises a specific implementation for the display phase of the pipeline from Chapter 4. An interactive technique for remote rendering of volume datasets is presented that allows for hiding latency and computation time by decoupling rendering and display phase. This is achieved by using an image-based rendering technique and 2.5D data from the remote server.

**Chapter 7** briefly summarizes the main contributions of this work, reviews its major conclusions and suggests opportunities for future research.

### 1.2 Motivation

The ubiquity of heterogeneous many-core systems in the recent years not only had an impact on codes that perform scientific calculations, but also on the visualization, which is the predominant part of the ensuing interactive post-processing phase and which is used to gain insights into the scientific data that originates from the simulation. Not only must the visualization algorithms keep pace with the steadily growing dataset sizes that result from scientific simulations, but also with the need of the scientist to explore the simulated data interactively.

In the second half of the last century, high performance computing (HPC) systems were usually used in a batch fashion, i. e. the scientist submitted a compute job, which would later be scheduled for execution and would even later write its results to a mass storage system from which the scientist could retrieve them. While this mode of execution is still the common case in HPC even today, many scientists wish to adapt their simulation at run time based on the inspection of intermediate results. In such scenarios, visualization can help as a means of inspection to create a feedback loop to adapt simulation parameters. Quite often, in such cases it is not desirable or infeasible to copy scientific data from the high performance computing system to the client computer the scientist uses. Designing visualizations that run on the same system as the simulation does can be challenging. On top of that, having to display the data on a computer at a remote location introduces an additional source of overhead and adds heterogeneity to the overall system.

Direct Volume Rendering (DVR) denotes a family of algorithms that can be used to display a wide variety of three-dimensional datasets. Many simulation codes produce results that can be rendered using this family of algorithms or generate outputs that can be resampled to be renderable with DVR. Because of that, it is especially important to adapt DVR algorithms to run on heterogeneous many-core systems, which can be equipped with all types of processors and accelerators.

This thesis illuminates the various aspects that need to be considered when adapting DVR to many-core systems. These aspects include, amongst others, the different parallelization paradigms that the serial algorithms need to be adapted to and

considerations for hiding latency introduced by networks connecting the manycore system with the client computer the scientist is interacting with. Theoretical considerations are followed by concrete implementations which are then evaluated regarding their general fitness for the application in terms of the quality of the resulting images, as well as their performance in terms of execution time.

### **1.3** Contributions

The contribution of this work is divided into two separate areas:

- Advances in Parallel Direct Volume Rendering. Modern workstations and HPC systems expose several means for parallelization through add-in card-based coprocessors, programmable GPUs and fast network interconnect. With the advent of GPGPU computing, Multi-GPU systems became prevalent. This work proposes ways to exploit these means for interactive Direct Volume Rendering. Implementations for several modern hardware platforms are evaluated and combined into a flexible software architecture that facilitates Direct Volume Rendering on heterogeneous systems. The developed software is integrated into an open source visualization package and published along with it under an open source software license.

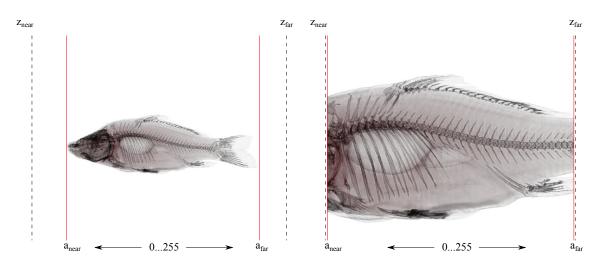

- Interactivity Techniques for Remote Volume Rendering. When frame rates drop significantly below 30 Hz, in Virtual Reality this can cause nausea and fatigue. Maintaining interactive frame rates can be a challenge in the context of remote visualization introducing network latency. An image-based interactivity technique for remote rendering is proposed that decouples the rendering phase from the display phase and is thus capable of hiding latency. The decoupling technique is specifically designed for Direct Volume Rendering and relies on heuristics to deduce a depth buffer from volume datasets to generate 2.5D data for remote display.

## Chapter 2

# Scientific Visualization

The need for visualization can generally arise in any scientific discipline. Natural sciences produce tremendous amounts of data from simulations and measurements. In that case, visualizations are needed that aim at a higher level of *abstraction* to filter the information that is beneficial from the information that doesn't carry any significant meaning. Engineering often aims at the *virtual reconstruction* of tools or machinery, whilst retaining their original proportions, so that they can e.g. be judged regarding *ergonomics*. Archaeologists may have an interest in *physical plausibility*, e. g. when lighting scenarios at ancient sites are simulated in order to understand the original lighting conditions. Artists may be interested in *photorealism*. That said, while the disciplines that develop a need for visualization are manifold, so are the methods that are used to fulfill those needs, and even further, while one type of visualization is suitable for one discipline, it may be counterproductive for the other. This thesis concentrates on visualization scenarios where datasets need to be visualized that are connected to a spatial description, i. e. their underlying topology can be mapped to points in 3D space. Rather than reaching for *photorealism* or physical plausibility, the primary aim of the algorithms investigated through the course of this thesis is to distinguish relevant from irrelevant information. Typical fields of application are *medical imaging* or *weather forecasting*. The family of algorithms that this thesis is centered around, Direct Volume Rendering (DVR), nevertheless, is not the primary focus of this chapter. Rather than that, this chapter

aims at motivating the general notion of scientific visualization, and it tries to devise a formal language to categorize the various types of scientific datasets, along with a broad overview of the general types of algorithms that are applicable to visualize some of those datasets. DVR is a tool that specifically aims at visualizing a certain subset of these datasets.

This introductory chapter is organized as follows. Section 2.1 briefly introduces and defines the notions *visualization* and *scientific visualization*. Section 2.2 provides a formal overview of scientific datasets alongside with a means to classify them regarding their spatial topology and the characteristic traits of the data items that make up the datasets. Section 2.3 reviews pipeline approaches to map data from measurements or simulation to specific visualizations. Section 2.4 gives an overview of some common visualization methods that can be used for the various kinds of datasets, and Section 2.5 gives a short introduction to the connection between scientific visualization and high performance computing (HPC), which is one of the key aspects of this thesis.

#### 2.1 Brief Introduction to Scientific Visualization

Visualization is a discipline that is concerned with the generation of images from general data. McCormick et al. [MDBZ87] define visualization as "[...] a method of computing (that) [...] transforms the symbolic into the geometric, enabling researchers to observe their simulations and computations. Visualization offers a method for seeing the unseen. It enriches the process of scientific discovery and fosters profound and unexpected insights." The authors also provided a coarse classification by subdividing visualization into the fields:

- Computer graphics

- Image processing

- Computer vision

- Computer-aided design

#### 2.1. BRIEF INTRODUCTION TO SCIENTIFIC VISUALIZATION

- Signal processing

- User interface studies

Hansen and Johnson [JH04] generally described the goal of visualization being "the creation of a visual representation to help explain complex phenomena" in their Visualization Handbook.

Earnshaw and Wiseman [EW92] postulated that "Scientific visualization is concerned with exploring data and information in such a way as to gain understanding and insight into the data. The goal of scientific visualization is to promote a deeper level of understanding of the data under investigation and to foster new insight into the underlying processes, relying on the humans' powerful ability to visualize."

For the purposes of this work, the term scientific visualization will be defined as follows.

**Definition 1 (Scientific Visualization)** Scientific visualization is the transformation of abstract data to a geometrical representation in order to gain a further understanding of the data. The need for scientific visualization stems, amongst others, from the humans' limited ability to perceive and imagine N-dimensional problem spaces and aims at narrowing these down to a more comprehensible depiction in the spatial domain of the simulation or the measurement performed to obtain the dataset in the first place. Scientific visualization is often, but not necessarily, aided by computation.

This working definition expresses several aspects in which the author's opinion differs from those of the authors of the aforementioned textbooks.

In contrast to McCormick et al., the author argues that visualization is not solely a method of computing but in general the result of human imagination, independent of the medium the individual uses to express his or her imagination.

This work's definition differs from that of Earnshaw and Wiseman in that it specifically does not state information as the entity to be visualized. Underlying this is a distinction between the notions *data* and *information* which assumes that data is uninterpreted. Raw data can however be converted to meaningful information through a cognitive process. In fact, the author argues that the process of visualizing data is one that actually facilitates this very transformation of abstract data to information, which is then accessible and useful to the scientist. This distinction is also reasonable in order to distinguish the field of scientific visualization from the large field of *information visualization*, which is not covered by this work. Scientific datasets are typically located in a spatial domain like in 2D or 3D space. In that case, the spatial context does not need to be deduced but is present *a priori*, which is in contrast to the datasets that are typically processed using information visualization.

For multi-dimensional datasets, i. e. datasets which may have an underlying spatial topology but exhibit single data items with a higher dimensionality than that of the space they are located in, the best mapping needs to be found that extracts the most relevant information regarding the parts of the data items pertaining to the remaining dimensions. Narrowing down the data to depict the relevant information in a perceivable way is of uttermost importance. Examples of multi-dimensional datasets can be found in turbulence simulation, where the simulation domain spans a spatial context and data items consist e. g. of velocity vectors in conjunction with pressure and particle emission. Visualizing multi-dimensional datasets can be accomplished by combining several of the techniques that are all but briefly motivated in Section 2.4.

### 2.2 Classification of Scientific Datasets

Scientific visualization methods are designed to explore various types of datasets differing in terms of their underlying *topology*, their *dimensionality* and their *time dependence*. In the following, a mathematical formalism to classify scientific datasets in terms of those properties is introduced.

In general, scientific datasets are made up of a finite set of *data items*, which are located in an N-dimensional Hilbert space. The topology of the dataset determines the connectivity of these data items in space and time. Specific manifestations of topologies are e. g. scattered topologies [CJ05], grid topologies [HLC91] or mesh

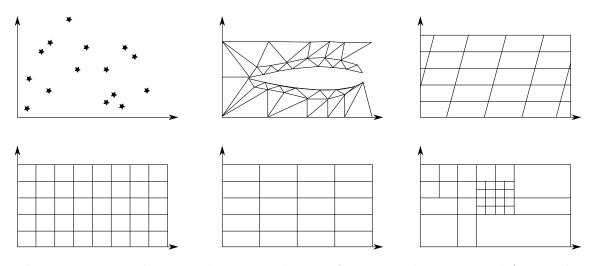

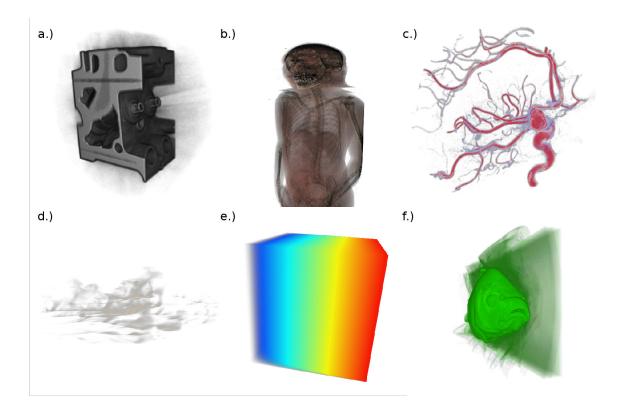

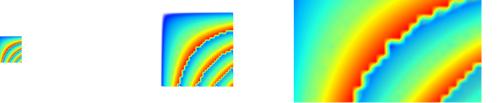

Figure 2.1: Topologies with varying degree of structuredness. From left to right, Top to bottom: scattered data, structured grid, regular grid, cartesian grid with equidistant spacing between vertices, rectilinear grid with equidistant spacing between vertices in each dimension, adaptive grid structure where nodes with a higher resolution emphasize regions of interest.

topologies [TYRG<sup>+</sup>06]. Grid topologies impose a cyclic, closed graph data structure on top of the dataset, where the locations of the data items are modeled as vertices and connections are modeled as edges. Grid topologies can be further classified into *structured* and *unstructured* grids, where structure implies a regular pattern of the connections between the data items regarding distances between vertices and angles between edges. In cases where the number of edges leaving a vertex cell is constant, one often refers to grid topologies in terms of the N - dimensionalgeometric primitive the edges connecting neighboring vertices form, resulting in terms like *rectangular* grids or *tetrahedron* grids. The volumetric regions spanned by the convex hull of these geometric primitives are referred to as *cells*. Figure 2.1 shows numerous examples of 2D topologies exhibiting varying degrees of structuredness. A good overview of topologies for scientific datasets is given in Chapter 7 of [JH04].

The dimensionality of scientific datasets on the one hand depends on the dimensionality of the Hilbert space the data items are located in. On the other hand, the dimensionality depends on the domain of the data items. Specialized scientific visualization methods exist for 2D and 3D spatial dimensions and for data items such as *scalars*, *vectors* or *tensors* [HPvW94].

Time dependent datasets typically exhibit time-varying data items. The topology of the dataset may also vary with time. This may have a varying impact on the way the dataset is stored and processed. Regular, adaptive grid topologies are used when the researcher exploring the dataset is especially interested in specific regions that are modeled using a higher grid resolution than the rest of the spatial domain. If these regions of interest are in motion, it may be possible to store the change of the grid with time as an *increment* of the previous time step and not having to store the whole topology anew for each frame. With unstructured grids, storing increments in general may be more difficult because of the weak connectivity of arbitrary grid cells. Anyhow, the dimensionality of scientific datasets that this thesis focuses on usually does not vary with time.

In accordance to this classification, a general way to analytically describe scientific datasets is by using tuples of the form (X, S, T), where X denotes the topology of the dataset, S stands for the data value at the grid position that depends on the dimensionality of the domain and  $T \in \mathbb{N} \setminus 0$  denotes time dependence.

For example, the tuple

$$((i,j,k),s), \tag{2.1}$$

$i, j, k \in \mathbb{N}$ , describes a 3D dataset located on a uniform grid, where each grid cell stores a scalar value and the dataset consists of only one time step.

The tuple

$$\left(\left(x_{i}, x_{j}\right), \left(v_{x}, v_{y}\right), t\right), \qquad (2.2)$$

$x_i, x_j \in \mathbb{R}, i, j \in \mathbb{N}$  can be used to express a dataset located on an unstructured grid, with multiple time steps storing vectors at each cell.

This mathematically formal description can be used to *generally* describe each type of the scientific datasets that the algorithms elaborated upon in this thesis are applicable to. In terms of a formal definition, the dataset is then a *function* of *space* and *time*,

which maps to a single variable or a higher dimensional codomain. Apart from that, this formal description makes no assumptions on how *actual values* of the function can be retrieved. For most nontrivial datasets, an analytical description is impossible to find. Datasets from measurement or simulation are usually available as a *set of tuples* for each specific data item. That said, in that case, it is the very nature of the dataset that there is a tuple for *every* data item in space, and for high resolutions of the underlying topology of the dataset, the amount of tuples can be tremendous. Because of that, apart from the formal description of a dataset in a mathematical sense, one also needs to consider the way that actual data items are stored, and the amount of data items that need to be visualized strongly influences the visualization algorithms that are applicable for the dataset. This thesis concentrates on algorithms that can cope with large grids that store tremendous amounts of data items.

### 2.3 Visualization Pipelines

In order to visualize datasets like the ones described above, post-processing steps are necessary to generate images from the abstract data items. Visualization pipelines often constitute the principal ground on which visualization systems are built. Frequently, the dataflow through the visualization pipeline is visually programmable e. g. by using a dataflow network. Examples of visualization software packages that facilitate this type of visual programming are ParaView (cf. Section 3.5.4)

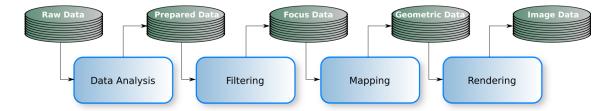

**Figure 2.2:** Haber McNabb visualization pipeline, enhanced with a data analysis phase as proposed by dos Santos and Brodlie. The data analysis stage is typically not interactive and is used to transition from multivariate or multidimensional data to data that can be visualized, e. g. by means of interpolation or a Principal Component Analysis.

and COVISE (cf. Section 3.5.6). Haber and McNabb [HM90] proposed a dataflow model that datasets must be subjected to in order to create displayable content. The pipeline comprises the stages

- **Filtering.** During filtering, raw data is filtered for items of interest. When e. g. the turbulent flow of water in a drainage system is simulated, sites like crossings or bends may be of higher interest because phenomena like eddies are likely to occur there, while plane bendings may be less interesting and are thus not considered for visualization. The filtering stage is often user controlled. The data after filtering is called *focus data*.

- Mapping. The mapping stage assigns positional information and properties like colors to the focus data from filtering. Often, the mapping step is actually a *remapping* step, e. g. if the original data was simulated on a rectangular grid, and is replaced with a hierarchical data structure that carries the same information but can be rendered more efficiently. The *geometric data* that results from this pipeline stage must be in a form that is e. g. suitable for one or a combination of the visualization algorithms described in Section 2.4.

- **Rendering.** At this stage, an actual image is created from the geometric representation that was obtained during mapping. Rendering is often hardware accelerated. Then, the implementation of the algorithm that is used must be capable of producing graphic primitives that are supported by the graphics hardware. As a result of this pipeline stage, image data in the form of pixels is generated, that can e. g. be written to the frame buffer.

One might argue that in some cases, the mapping step is obsolete or there is no clear distinction between mapping and filtering or mapping and rendering. For instance, if the simulation was performed on a grid in the first place, and this grid is now reused for rendering, a mapping to geometric data is unnecessary. On the other hand, post-classification transfer functions (cf. Section 2.4.4) map data values to colors after reconstruction, which is typically performed during rendering. Also, if hierarchical data structures are employed for filtering, e. g. to put a higher emphasize

on certain regions of interest and assigning more grid cells to those than to other regions, filtering actually implies a geometric mapping.

In 2004, dos Santos and Brodlie [dSB04] enhanced this model with a data analysis phase to address multidimensional data (cf. Figure 2.2). Dasgupta and Kosara [DK12] added a feedback loop to the visualization pipeline that is based on cognition and perception and that can be used to alter parameters of the various stages to adapt the rendered output dynamically. In general, the various stages of the pipeline are often implemented to be adapted interactively. For example, the process of finding an appropriate location for a cutting surface is a user controlled filtering step. The ensuing process of finding an appropriate mapping e. g. from densities to colors is also often guided through user interaction, and during rendering the user usually interacts with the dataset by adjusting camera parameters like view point and zoom. If the user is not satisfied with the result, she may return to any of the pipeline stages and make adjustments.

#### 2.4 Visualization Methods for Scientific Datasets

This section introduces some of the more commonly used methods to visualize scientific datasets. As there is an overwhelming variety of visualization methods applicable to the numerous kinds of datasets described above, this section only presents a small, representative selection of visualization algorithms. The section mainly focuses on visualization methods aimed at 3D datasets with an underlying grid topology. The family of DVR algorithms, which also falls under this category, will be covered in more detail in Chapter 3 and is thus omitted from this section.

#### 2.4.1 Contouring

Contouring algorithms extract isolines from 2D datasets or isosurfaces from 3D datasets. Contours are extracted by defining an *isovalue* that falls in the range of possible data values and which is used to determine which data items are on the inside or on the outside of the contour. Generally speaking, given a dataset

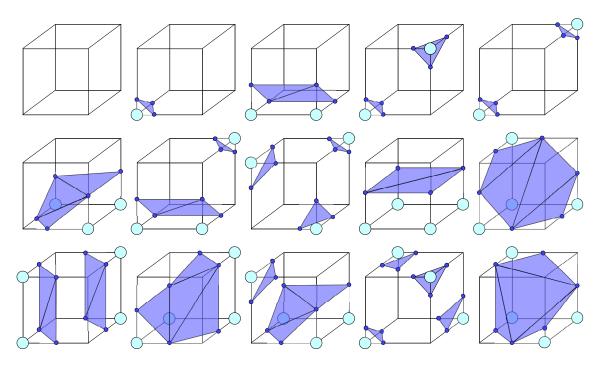

Figure 2.3: Marching cubes contouring algorithm: the patterns are used to derive the 256 possible ways an isosurface may intersect a box through permutation.

(X, S, T), contouring algorithms hence extract only those parts of the dataset where S takes on a specific value  $c \in S$ , for arbitrary X and arbitrary T. In the 3D case, the contour then represents the infinitesimally thin transition between two different media. Contours are typically extracted as part of an offline process and are then converted e. g. to a polygon mesh that can be rendered with graphic acceleration. The Marching Cubes Algorithm [LC87] is a famous representative of the family of contouring algorithms for the 3D case. An isosurface is extracted by independently processing the cuboid cells of a uniform 3D grid. The eight data values at the vertices of each cuboid are evaluated to be on the inside or on the outside of the isosurface using the isovalue. If one of two neighboring vertices is on the inside and the other one is on the outside, the exact location where the isosurface intersects the connecting edge is approximated using linear interpolation. Only a limited edge configuration can possibly be intersected by the isosurface, so that the triangulation for each configuration, that is necessary for edge generation, can efficiently be stored in a lookup table. All 256 possible cases can then be obtained as a permutation of one of the 15 patterns depicted in Figure 2.3. Unit normals are necessary for

shading calculations. These are obtained by calculating central differences for the box vertices. From these, normals for the triangle vertices can also be calculated using linear interpolation.

#### 2.4.2 Slicing

Slicing or *cutting* in general is a process that extracts a lower order representation from a higher order representation by leaving out information. Slicing algorithms are quite often combined with a facility for *probing*, which requires the visualization algorithm to run interactively and enables finding an appropriate location e.g. of a 3D cutting geometry through user interaction. Generally, in a common slicing scenario a dataset (X, S, T) is given, with arbitrary X, S and T. Further a proxy representation (Y,T) is given. The algorithm then proceeds by extracting only those values from the original dataset for visualization where  $x = y, x \in X$  and  $y \in Y$ . This is usually followed by a mapping process to colorize the extracted data, e. g. by using contouring (cf. Section 2.4.1) or color mapping (cf. Section 2.4.4). Quite often, (Y, T) is a plain represented through a normal  $N \in Y$  and an anchor position  $P \in Y$ , and  $Y = \mathbb{R}^3$ . It is safe to say that the most common usage scenario of slicing algorithms is one where  $X = \mathbb{R}^3$  and  $Y = \mathbb{R}^3$ , i. e. information is extracted from a 3D dataset using a 3D cutting surface. In contrast to contouring, where information was extracted based upon evaluating S to have taken on a certain value, slicing algorithms extract information based on spatial location X.

#### 2.4.3 Particle Tracing

Yet another family of visualization algorithms is *particle tracing*, where the aim is to extract information that is related to the progression of data items over time  $t \in T$ . Particle tracing is used to extract *trajectories* from *vector fields*. Generally, datasets of the type (X, S, T), where  $t \in T > 1$ , can be meaningfully used to perform particle tracing. Furthermore, most often  $S \in \mathbb{R}^3$  is a vector space that represents velocity. Particles are then *released* into the velocity *vector field* at positions  $y_t \in Y, t \in T$ . The initial positions are called *seed points*. If  $y_t \in X$ , y is *subjected* by the vector field and a new position  $y_{t+1}$  is computed using integration. The integration order will directly influence the fitness of the position estimate. Fourth order integration like it is performed using the *Runge-Kutta method* [Bak77] has proven to provide stable computational results. Particle tracing algorithms can be distinguished based upon the way that actual trajectories are depicted over the course of time. *Pathlines* show the whole paths that particles follow after being released into the vector field, until eventually leaving it. *Streamlines* represent only the local orientation of particles in an instance of time. Most recently, with the advent of general-purpose programming capabilities of GPUs, particle tracing implementations have become feasible [Bus11] that allow not only for interactively setting seed points, but also for interactive trajectory computation.

#### 2.4.4 Color Mapping

Color mapping provides a means to express certain information by assigning color to specific properties of data items. In case of simple color maps, a color is provided for a specific data value using a lookup table. The data values are usually scalar to obtain reasonable sizes for the lookup table.

Quite often, a general mapping

$$t: D \to \mathbb{R}^c \tag{2.3}$$

from the data domain D to a visual spectrum  $\mathbb{R}^c$  is desired. Most often, the spectrum is represented by a color space like RGB, so that a common case implies that c = 3. Such functions, which map data values to colors are called *transfer functions*. Since the mapped colors are not useful on their own but depend on a proxy representation, transfer functions are used in conjunction e. g. with one of the visualization methods introduced in this section. In the case of slicing, it usually suffices or is even desirable to only map from data values to colors.

In the context of Direct Volume Rendering algorithms, which this thesis is focused on and which are the gist of the ensuing chapter, on top of that, a mapping

$$t: D \to \mathbb{R} \tag{2.4}$$

from data values to transparency is desirable in addition to mere color mapping. In addition to that, there is in general no restriction regarding which kind of data should be mapped to colors or transparency. In the presence of *fields*, e. g. the *gradient* may be a trait of interest that can be mapped and can provide further insight at regions where different media transition.

Some visualization algorithms like slicing or Direct Volume Rendering rely e. g. on trilinear or higher-order interpolation to reconstruct the dataset between grid cells. Transfer functions can then be applied *pre-interpolative*, i. e. to the actual data items of the grid, or *post-interpolative*, i. e. to the interpolated data sample. Since transfer function application is often referred to as *classification*, the classification order is often referred to using the terms *pre-classification* and *post-classification*. Hadwiger et al. show in Chapter 4 of [HKRS<sup>+</sup>06], that post-interpolative transfer functions are better suited for reconstruction of datasets containing high frequencies.

Transfer function design, specifically in conjunction with DVR, is a research topic on its own because the task of finding a useful mapping from a field to colors and opacities tends to be challenging for users, that typically are no computer scientists, but rather surgeons or neurologists, which rely on transfer functions to distinguish e. g. a tumor from healthy tissue. Automatic transfer function design [KD98] [ZT09] [RBB<sup>+</sup>11] can be useful if a bulk of datasets is processed or if for any other reason a thorough review of each dataset through the user is impractical or not possible at all. Quite often, the default transfer function used in visualization systems is the rainbow color map, which maps data items to highly saturated colors. Alternatives were proposed which also take perceptual considerations into account [Mor09].

### 2.5 Scientific Visualization and High Performance Computing

Scientific visualization and HPC are interdependent in that on the one hand, visualization is typically the predominant step of the interactive post-processing phase of simulations, and on the other hand because it relies on resources that allow for interactive computation of the algorithms involved in visualization. With an increase in the compute resources that are available for visualization, parts of the visualization pipeline outlined above can be implemented interactively, which was impossible so far. For example, with the advent of general-purpose computing capabilities on GPUs (see Section 3.3.4), contouring algorithms or particle tracing can be computed in real-time under certain conditions [Bus11] [AW13]. With GPUs becoming available as cluster resources, and graphics researchers using programming paradigms like message passing or multithreading, the interdependence between the two disciplines grows to an even higher degree. Under these conditions, concepts to optimize the communication patterns during post-processing need to be iterated. If e. g. significant parts of the visualization pipeline are performed on an HPC system, remote rendering (cf. Chapter 6) can be employed, and bandwidth issues must be taken into consideration. In situ visualization is a concept that aims at providing a feedback loop to interactively monitor intermediary results in order to adjust parameters of an ongoing simulation.

From the development of the recent years, it seems clear that the two disciplines, scientific visualization and high performance computing, must be considered in conjunction rather than as two separate research areas. The book edited by Bethel et al. [BCH12] provides a general overview of the concepts involved when intermingling the realm of scientific visualization with that of HPC. Many of the concepts introduced there, like e. g. sort-last compositing, are highly relevant for this thesis. In contrast to being general about mixing scientific visualization and HPC, this thesis focuses on Direct Volume Rendering specifically. The ensuing chapter focuses on the current state of the art in Direct Volume Rendering on HPC systems. While Chapter 4 devises a software architecture for volume rendering on HPC systems, concrete implementations are proposed and evaluated in Chapters 5 and 6.

### Chapter 3

# State of the Art in Parallel Direct Volume Rendering

Section 2.2 proposed a notation to describe scientific datasets as a function of their topology, their dimensionality and their time dependence. Some subset from the huge selection of available algorithms for scientific visualization was introduced that is applicable to various kinds of scientific datasets.

The following section concentrates on a set of algorithms that are used to implement one specific visualization technique called Direct Volume Rendering (DVR). That technique is used to *directly* render datasets of the general form

$$(X, S, T), X \in \mathbb{R}^3, S \in \mathbb{R}^n \text{ and } T \in \mathbb{N}.$$

(3.1)

Direct rendering in this case means that a direct mapping from the data domain to the image plane is preferred over e. g. *explicitly* extracting a representative geometry like an isosurface first and rendering that afterwards. Although DVR is applicable to general grid topologies, and although algorithms like e. g. ray casting (see Section 3.2.6) in its general form or cell projection (see Section 3.2.5) specifically support unstructured grid types, the datasets of interest in this thesis typically are of the form

$$(X, S, T), X \in \mathbb{N}^3, S \in \mathbb{R} and T \in \mathbb{N}.$$

(3.2)

Note that hierarchical grid types can be completely described by combining uniform grids using a *divide and conquer* strategy. Uniform grids and their hierarchical "siblings" typically originate from medical imaging methods such as magnet resonance tomography (MRT) or X-ray computed tomography (CT), or from simulations like the ones used in astrophysics or meteorology.

This chapter begins with a description of the physical phenomena involved when light interacts with participating media in a volume of space, resulting in an integral equation (the *scattering equation*), that DVR algorithms seek to solve incrementally. In the following, the current state of the art in sequential DVR algorithms is presented. This is followed by a brief recapitulation of the general parallel programming models that are used to optimize for different hardware platforms. Then a description follows on how these programming models can be used to parallelize the various sequential DVR algorithms. The chapter concludes with an overview of actual DVR implementations that can be found in current visualization systems.

#### 3.1 Introduction to Direct Volume Rendering

The following section provides the reader with an introduction to the kind of problems solved with Direct Volume Rendering, as well as with a brief overview of how DVR is typically implemented on modern hardware. A more comprehensive overview of methods for real-time DVR and their theoretical background can e. g. be found in the textbook by Hadwiger et al. [HKRS<sup>+</sup>06]. This section on the optical models underlying DVR is loosely based upon this textbook, as well as on the paper by Max [Max95] and the chapter on DVR and transfer function pre-integration from the Visualization Handbook [JH04].

DVR is a visualization technique that is typically used to display 3D fields. The data items at each discrete location of the 3D field are often, but not necessarily, scalars. The topology of the 3D field is expressed through a 3D grid. DVR in its

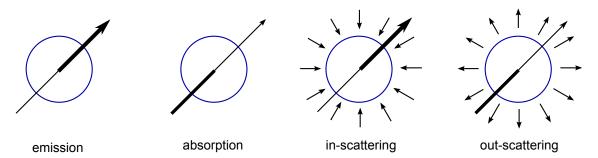

Figure 3.1: Phenomena involved in the interaction of light traveling along a ray, and the matter that is contained by the medium that the ray travels through. The depiction is inspired by Figure 1.3 from Hadwiger et al. [HKRS<sup>+</sup>06]. Emission of radiative energy is due to heat that originates from light interacting with matter. Absorption is the opposite phenomenon, where radiative energy is transformed into heat. Scattering phenomena are usually evaluated probabilistically and also result in energy associated with the light ray being increased or removed.

general form is used interdisciplinarily, with applications coming e. g. from medicine, engineering or natural sciences. As stated in [BCH12], DVR algorithms generate images from volume data without explicit geometry extraction. Although being computationally more expensive, direct rendering methods prevent information loss. On top of that, parameters like isovalues, since being applied to the data directly, are typically implemented using table lookups and thus do not impose execution halts e. g. for extracting a new isosurface.

DVR methods aim to solve the scattering equation [KVH84]. The scattering equation stems from geometric optics and provides a physically approximate basis to describe the interaction of light and matter from the participating medium that light is traveling through. This is typically expressed in terms of the following phenomena (cf. Figure 3.1) that light running along a straight line interacting with matter is subject to.

- **Emission.** A heated body emits radiation, and some of the emitted radiative energy possibly falls in the frequency of visible light.

- **Absorption.** Radiative energy that can be encountered along the light ray interacts with the medium and is converted to heat.

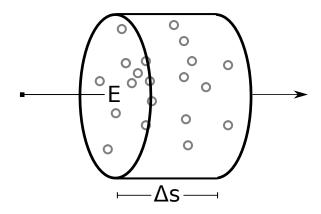

Figure 3.2: Schematic that physically motivates the light-matter interaction models introduced in this section. In the limit, when  $\Delta s$  goes to 0, absorption, emission and scattering become proportional to the projected area of the particles.

- **In-Scattering.** Radiative energy from the medium is scattered towards the light ray, resulting in an increased amount of energy associated with the ray.

- **Out-Scattering.** Radiation that is located along the path of the light ray is scattered towards the outside of the participating medium. Thus, energy is removed from the ray.

The following mathematical formulation of the aforementioned phenomena that eventually results in a construct called the *volume rendering integral* is based on Max 1995 [Max95] and Section 8.1 of [JH04], which is basically a summary of the aforementioned publication.

The probability of light being emitted, absorbed or scattered along a ray is in the following considered to be proportional to the amount of particles  $\rho$  per unit volume along the direction  $\omega$  of the ray. Particles are considered to be spherical with projected area  $A = \pi r^2$ . The particles flow through a cylinder having a base of area E and a length of  $\Delta s$ . Thus the cylinder contains  $N = \rho E \Delta s$  particles per unit of time t (cf. Figure 3.2).

Let  $\Delta s$  now tend to 0. Then, in a model that takes *only absorption* into account, the light intensity gathered along the ray at distance s is described by the differential equation

#### 3.1. INTRODUCTION TO DIRECT VOLUME RENDERING

$$\frac{dI}{ds} = -\tau(s) I(s), \qquad (3.3)$$

which can be analytically solved as follows:

$$I(s) = I_0 e^{-\int_0^s \tau(t)dt}.$$

(3.4)

$I_0$  denotes the light intensity at s = 0, i. e. the position where the ray enters the volume, and  $\tau = A\rho$  denotes the *extinction coefficient*.

The term that  $I_0$  is multiplied with,

$$T(s) = e^{-\int_0^s \tau(t)dt},$$

(3.5)

is called the *transparency* at position s. The *absorption only* model thus describes the influence of the medium at each continuous position s acting upon a background light source.

Assuming that the particles now glow diffusely and letting  $\Delta s$  go to 0 again, the *emission only* model can be described by the differential equation

$$\frac{dI}{ds} = C(s)\rho(s)A = C(s)\tau(s) = g(s), \qquad (3.6)$$

with the source term g(s) accounting for glow that adds energy scattered towards the eye along the direction of the ray. Solving this differential equation yields

$$I(s) = I_0 + \int_0^s g(t) \, dt.$$

(3.7)

Combining the two models yields the absorption plus emission model

$$\frac{dI}{ds} = g(s) - \tau(s) I(s)$$

(3.8)

and its analytical solution

$$I(s) = I_0 e^{-\int_0^s \tau(r)dr} + \int_0^s g(t) e^{-\int_t^s \tau(r)dr} dt.$$

(3.9)

In this model, the background light is attenuated, and emitted energy is scattered towards the eye. The emitted energy is then itself attenuated by the opacity that was already *gathered* along the ray so far.

In addition to emission and absorption, external illumination is usually accounted for by evaluating a local shading formula such as the Lambert formula for diffuse or the Phong formula for specular lighting [Pho75] at positions where the ray interacts with the medium. The normal needed to evaluate such lighting models is usually approximated by calculating the gradient  $\nabla f(x, y, z)$ . The gradient for an arbitrary position in the medium is usually estimated by using central differences in a region  $[f(x, y, z) - \delta, f(x, y, z) + \delta]$ , i. e.

$$\nabla f(x,y,z) = \frac{1}{2\delta} \begin{pmatrix} f(x+\delta,y,z) + f(x-\delta,y,z) \\ f(x,y+\delta,z) + f(x,y-\delta,z) \\ f(x,y,z+\delta) + f(x,y,z-\delta) \end{pmatrix}$$

(3.10)

(cf. [HKRS+06], Section 5.3).

Local illumination is then calculated at position X as

$$S(X,\omega) = r(X,\omega,\omega') i(X,\omega'), \qquad (3.11)$$

where  $r(X, \omega, \omega')$  is a bidirectional reflection distribution function (BRDF),  $i(X, \omega')$  is the incoming light intensity at position x from direction  $\omega'$ , and  $\omega$  is the direction into which light is reflected.

Local illumination usually only contributes if the gradient magnitude is well defined at the respective sampling position. Otherwise, the local illumination term is set to 0 and only emission and absorption are accounted for. Local illumination is combined with the emission and absorption model by adjusting the source term g from above to account for non-directional glow E(X) and the single-scattering term  $S(X, \omega, \omega')$ :

$$g(X,\omega) = E(X) + S(X,\omega)$$

(3.12)

More complicated models adjust the source term g to account for multiple scattering as well. Evaluating multiple scattering involves finding the intensity at *each* position x in *each* direction  $\omega$ , so that the source term at distance s becomes

$$g(s,\omega) = \int_{4\pi} r(X = s\omega, \omega, \omega') I(X - s\omega, \omega') d\omega', \qquad (3.13)$$

which integrates the incoming light from all directions on the unit sphere. Only more recent publications concentrate on producing images accounting for multiple scattering in real-time [ASW13] [ZM13], while typical real-time implementations incorporated into popular visualization systems (cf. Section 3.5) usually only account for emission, absorption and local illumination at best.

Because there exists no analytical solution to the scattering equation for nontrivial datasets, the problem is usually discretized e. g. by substituting a Riemann sum for the integration. Consider the absorption plus emission model represented through Equation 3.8. The integral underneath the continuous curve representing the extinction coefficient  $\tau(s)$  can be approximated using a sum:

$$\int_0^s \tau(r) dr \approx \sum_{i=1}^n \tau(i\Delta x) \Delta x, \qquad (3.14)$$

where  $\Delta x = \frac{D}{n}$  is the step size and *n* is the number of steps necessary to march a ray from the outermost edge of the volume at position 0 to the eye at position *D*.

Further, from the rule of exponents it follows that

$$e^{-\sum_{i=1}^{n}\tau(i\Delta x)\Delta x} = \prod_{i=1}^{n} e^{-\tau(i\Delta x)\Delta x}.$$

(3.15)

Similar considerations hold for the rest of Equation 3.8, which can then approximately be solved using the following system of Riemann summations:

$$I(D) \approx I_0 \prod_{i=1}^n t_i + \sum_{i=1}^n g_i \prod_{j=i+1}^n t_j,$$

(3.16)

where  $t_i = e^{\tau(i\Delta x)}$  and  $g_i = g(i\Delta x)$ .

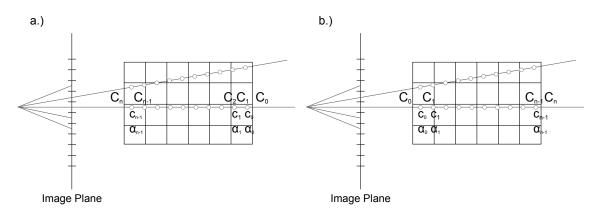

Applying some further transformations and letting  $\alpha_{src} = 1 - T(s)$  (i. e. reformulating Equation 3.16 in terms of opacity rather than transparency), this yields the basic operation that is necessary to compose an image from a discretized version of the scattering equation: alpha compositing. The compositing equations provide calculation rules to derive color and opacity based on the order in which volume samples are blended to form a final image. The compositing equations apply to all of the DVR algorithms described in Section 3.2. They are independent of the type of decomposition that the algorithm requires to evaluate the scattering equation - some of the algorithms rely on an image space decomposition, while others rely on an object space decomposition. Nevertheless, depending on the traversal order in which e. g. a ray or a slicing plain is traversed through the volume, either the front-to-back compositing equation

$$C_{dst} = C_{dst} + (1 - \alpha_{dst}) \alpha_{src} C_{src}$$

$$\alpha_{dst} = \alpha_{dst} + (1 - \alpha_{dst}) \alpha_{src}$$

(3.17)

or the back-to-front compositing equation

$$C_{dst} = \alpha_{src}C_{src} + (1 - \alpha_{src})C_{dst}$$

$$\alpha_{dst} = \alpha_{src} + (1 - \alpha_{src})\alpha_{dst}$$

(3.18)

applies, where  $C_{src}$  is the color portion of the incoming radiance,  $C_{dst}$  is the radiance that was already accumulated,  $\alpha_{src}$  is the opacity associated with the sampling position and  $\alpha_{dst}$  is the accumulated opacity.

The relationship between the two compositing equations, which are also referred to as the *under*-operator (front-to-back) and *over*-operator (back-to-front) [PD84], and the emission and absorption model can also be seen by representing the exponential from Equation 3.4 as a Taylor series expansion:

$$I(s) = I_0 e^{-\int_0^s \tau(t)dt} = I_0 \left( 1 - \tau(s) + \frac{(\tau s)^2}{2!} - \frac{(\tau s)^3}{3!} + \dots \right) \approx I_0 \left( 1 - \tau(s) \right)$$

(3.19)

(cf. Section 8.2.1.2 of [JH04]), which corresponds to accounting for absorption by multiplying  $C_{dst}$  and  $\alpha_{dst}$  by  $(1 - \alpha_{src})$ .

When accumulating opacity by e. g. marching a ray through the volume density using Equations 3.17 or 3.18 to evaluate the sums from equation 3.16, the *sampling* frequency n must be chosen appropriately (i. e. according to the sampling theorem, see e. g. [FvDFH90] and the remarks regarding pre-integrated classification below). Anyway, for the time being, consider n to be chosen arbitrarily, e. g. based on a performance measurement that is used to maintain a certain, fixed frame rate at run time and adjusts n accordingly. Because n directly affects the ray marching step size D/n, decreasing n will result in the overall opacity to decrease because the extinction coefficient is obtained through a transfer function lookup, and the result from that lookup is absolute rather than relative to the step size. This is reasonable regarding a continuous integration but will result in inconsistencies with Riemann summation. Then an opacity correction step that adjusts the absolute opacity to the step size is necessary [LCNC98] [KLT07]:

$$\alpha' = 1 - \sqrt[n]{1 - \alpha}.\tag{3.20}$$

Alternative compositing schemes not based on the scattering equation exist. Max-

imum intensity projection (MIP) [HMS95], which is e. g. used for X-ray imaging, assigns the color of the volume sample with the highest intensity:

$$C_{dst} = max \left\{ C_{dst}, C_{src} \right\}.$$

(3.21)

This compositing scheme in general is less computationally intensive because there is no need to sort for front-to-back or back-to-front evaluation (neglecting bandwidth considerations that possibly mandate a coherent traversal order). On the other hand, by neglecting the traversal order when weighing the volume samples encountered during volume traversal, natural depth cues are not accounted for, that would otherwise result from attenuation through volume density in front of the current sample. While the focus of this thesis is on DVR algorithms that employ alpha compositing, adapting to alternative compositing schemes like MIP can be implemented intuitively by substituting only a few calculations, especially if the alternative compositing scheme is order-independent.

Deciding for one of the two traversal orders has certain implications concerning the reliability of the final image as well as on optimization opportunities that exist for certain algorithms. Given that the discretized evaluation of the scattering equation is performed with limited floating-point precision, the result obtained through front-to-back compositing will in general be different from the result obtained through back-to-front compositing. This is because the addition operation (+) and the multiplication operation  $(\times)$  for floating-point numbers in general do not have the associative property. Because of the iterative nature of the two compositing equations, round-off errors will grow more severe because of accumulation. With the front-to-back compositing scheme, samples near the viewing position will affect the final image to a higher degree, while it is the other way around with back-to-front compositing. The influence of the round-off errors will increase with increasing sampling rates. Front-to-back compositing can facilitate the implementation of the early-ray termination optimization strategy (cf. e. g. [MIH04]).

Engel et al. [EKE01] proposed to enhance DVR using a technique called *pre-integrated classification*. From the sampling theorem follows that a signal can only be reconstructed if it is band-limited and if sampling frequencies higher than the

Nyquist frequency, i. e. twice the frequency of the original signal, are used for sampling [FvDFH90]. However, if the term  $\tau$  (s) from Equation 3.8 is obtained from a transfer function, reconstruction of the original signal results in not only having to sample the 3D volume data, but also the transfer function which potentially contains high frequencies too. With the naive approach, the appropriate sampling frequency is proportional to the Nyquist frequency of the volume *times* the Nyquist frequency of the transfer function. With pre-integration, however, opacity as a function of two sample positions  $s_1$  and  $s_2$  and the length of the line segment spanning  $s_1$  and  $s_2$ is pre-calculated and then stored in a lookup table. This lookup table is then used instead of the post-classification lookup that would usually have been performed. That way, the appropriate sampling frequency is only proportional to the frequency of the volume dataset. Pre-integrating the transfer function thus helps to reduce round-off errors and to increase performance because of the lower sampling frequency necessary. Pre-integrated classification in general is applicable to each of the DVR algorithms motivated in the following section.

# **3.2** Direct Volume Rendering Algorithms

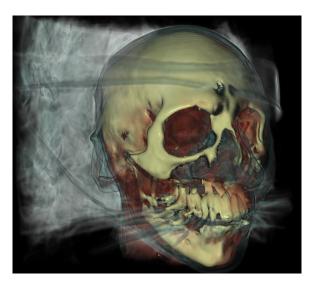

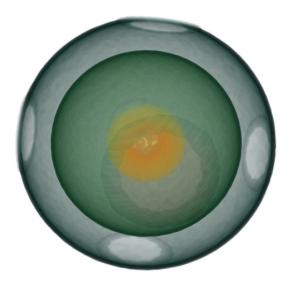

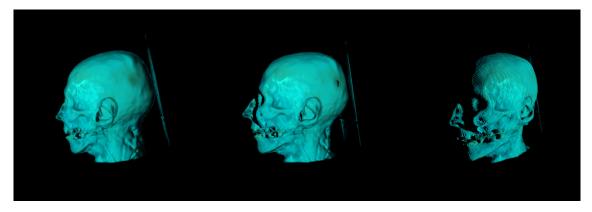

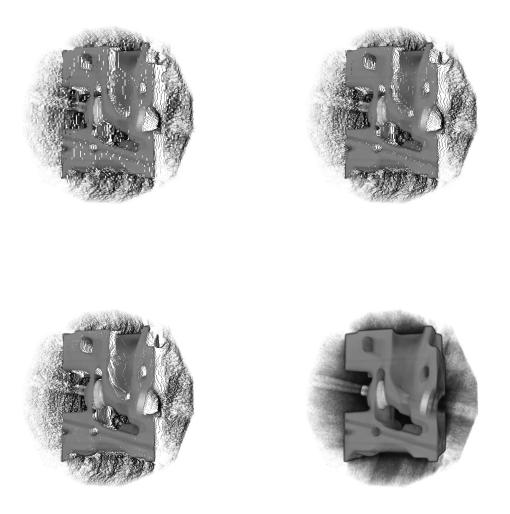

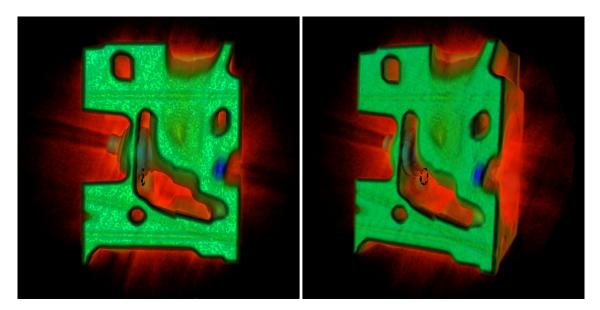

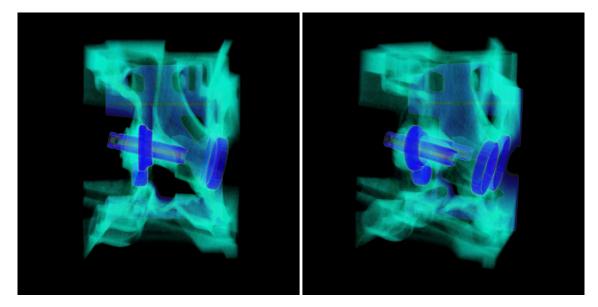

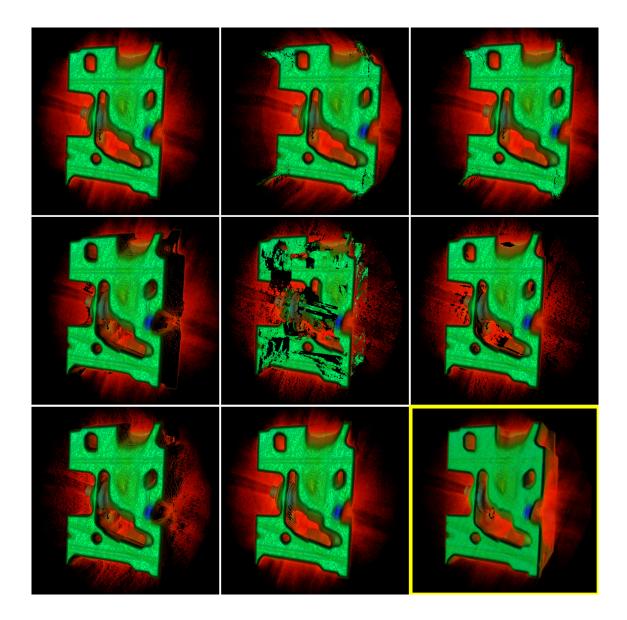

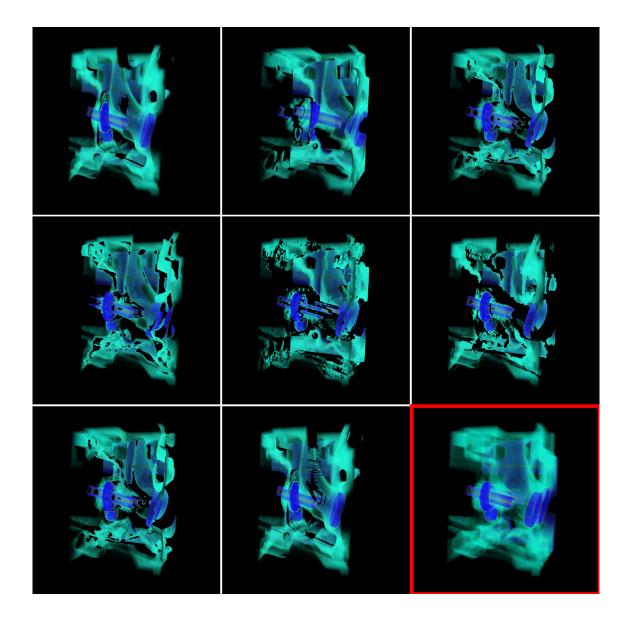

An interactive solution to the scattering equation laid out in the previous section is only possible to obtain for trivial problems. In more realistic cases, a trade off is necessary between interactivity and the physical correctness of the output image. Interactive DVR algorithms often only take the absorption and emission term of the scattering equation into account. Scattering phenomena are often simplified to single-scattering only. Figure 3.3 shows a medical dataset obtained from a computed tomography that is rendered using DVR and local illumination with the Blinn-Phong reflectance model [Bli77].

The following subsections summarize algorithms for interactive DVR. Being designed to target different hardware platforms, these algorithms are part of visualization systems that are widely used by researchers. Each algorithm either relies on a decomposition of the volume dataset in object space or on a decomposition of image space for display.

Figure 3.3: Computed tomography medical dataset rendered using DVR, with a local illumination model applied.

# 3.2.1 Texture-Based Volume Rendering

Texture-based Direct Volume Rendering algorithms are specifically designed for hardware with texture mapping capabilities like GPUs or dedicated graphic workstations. The first authors to propose texture-based DVR algorithms were Hastreiter et al. [HÇE96] and later Westermann and Ertl [WE98] or Dachille et al. [DKC<sup>+</sup>98]. Krüger et al. [KW03] provided an overview of how to implement texture-based approaches on modern GPUs. A thorough overview can also be found in the aforementioned textbook by Hadwiger et al. [HKRS<sup>+</sup>06].

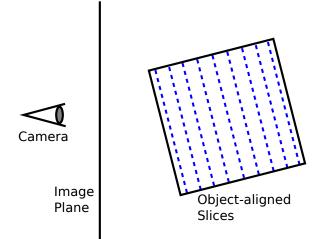

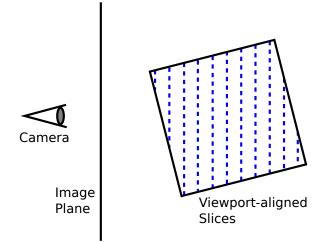

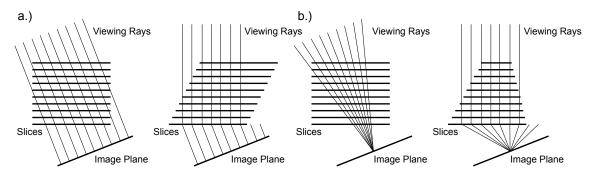

Texture-based approaches decompose object space into a set of surfaces that in the following will be referred to as a *proxy geometry*. Graphics hardware primitives are usually planar. Thus the proxy geometry usually consists of polygons, albeit composite geometries like e. g. spherical shells [LMHJ99] [KW03] were proposed as well. In the latter case, the spherical shells are constructed using tesselation. In the more usual case using a planar proxy geometry, polygons are rendered in back-to-front or front-to-back order. The individual polygons constituting the proxy geometry are often referred to as *slices*. Two methods are prevalent: *object-aligned slices* used with 2D texturing and *viewport-aligned slices* used with 3D texturing.

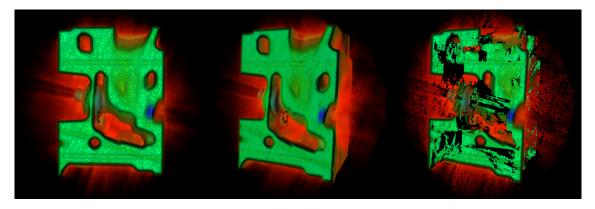

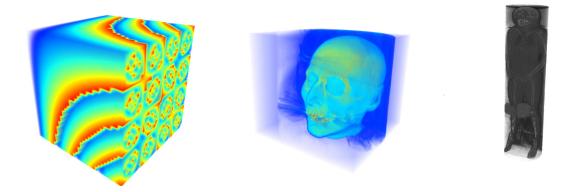

Figure 3.4: Object-aligned slicing. Slices are drawn parallel to the object axes of the volume dataset. Colors and transparency are assigned from 2D textures. Quadrangles can be precomputed and 2D texture lookup is more efficient than 3D texture lookup. On the downside, bilinear interpolation will result in a poor reconstruction of the 3D function inherent to the volume dataset.

Object-aligned slicing (cf. Figure 3.4) samples the volume datasets in object space using pre-calculated quadrangles. The quadrangles are drawn parallel to one of the object axes of the volume dataset. The volume dataset is organized into a set of 2D textures with one texture per quadrangle. The 2D textures provide colors and transparency values obtained e. g. by applying a transfer function (cf. Subsection 2.4.4). Then the quadrangles are rendered in back-to-front or front-to-back order while applying the appropriate compositing equation. The continuous function represented by the volume dataset is typically reconstructed using bilinear interpolation, which can be performed fast by modern graphics hardware. This approach has several disadvantages. 2D textures provide fast lookup using bilinear interpolation but will result in a poor reconstruction compared to e.g. trilinear interpolation using 3D textures. Another shortcoming of the object-aligned slicing approach are visual artifacts that become visible if the volume dataset is rotated so that the axis the slices are drawn along is almost perpendicular to the normal of the image plane. In that case, the volume dataset appears to have holes because one can see through the quadrangles used as proxy geometry. This shortcoming can be mitigated by having one stack of quadrangles and textures per object axis and flipping depending upon

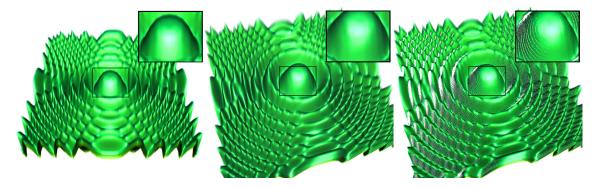

Figure 3.5: Viewport-aligned slicing. Slices parallel to the image plane are used to sample a 3D texture. Intersection polygons need to be recreated each time the virtual camera moves. 3D texturing enables trilinear or higher-order reconstruction kernels.

the angle between object coordinate axis and the normal to the image plane. While the hole artifacts can be hidden this way, each time the quadrangle stack gets flipped, the appearance of the image will change recognizably due to compositing accuracy and due to the fact that the direction in space of the bilinear interpolation operation changes. On top of that, the memory requirements triple with this approach.

The term *viewport-aligned slicing* is a bit misleading because it suggests that slices are actually quadrangles that are aligned to the four corners of the virtual viewport entity maintained by graphics application programming interfaces (APIs). In contrast to that, the technique referred to as viewport-aligned slicing assumes that object space is sampled using planes that are parallel to the image plane (cf. Figure 3.5). Because the term viewport-aligned slicing is used throughout the literature, this expression is adopted by this work, anyway.

With slices parallel to the image plane, the proxy geometry cannot be precomputed. In general the proxy geometry will also not consist of quadrangles only. The proxy geometry is created by sampling the volume using parallel planes with equal distances. For each plane the intersection with the bounding box of the volume dataset needs to be calculated, which result in either a triangle, a quadrangle, a pentagon or a hexagon. Like in the object-aligned slicing case, alpha compositing can then be performed in back-to-front or front-to-back order. Texture coordinates are calculated for the vertices of the intersecting polygons which are used to lookup colors and transparency values from a 3D texture. The continuous function represented by the volume dataset can be reconstructed using trilinear interpolation which is implemented by the fixed function pipeline of modern graphics hardware. Higher-order reconstruction kernels like e. g. tricubic interpolation can also be applied using programmable graphics hardware. Reconstruction using 3D textures will typically be slower than sampling 2D textures, but will in general produce more faithful results.

In order to speed up the proxy geometry generation process, portions of the boxplane intersection calculations can be transferred to the GPU. Rezk Salama and Kolb [RSK05] proposed to perform the intersection test in a vertex program. They employed this optimization to load balance the fragment stage of the rendering pipeline and the vertex stage, with the latter potentially being starved on GPUs that in these days did not yet implement a unified shader architecture. In their case, six vertices need to be transferred to the GPU per box per plane. If the intersection test produces a polygon consisting of less vertices, identical vertices will be generated. Duplicate vertices will result in degenerate triangles which will not contribute to the fragment stage of the rasterization pipeline. Zellmann and Lang [ZL13] showed that the proxy geometry generation can be accelerated by distributing the box-plane intersection calculations among a vertex program and a geometry program. Fast box-plane intersection tests are crucial if the volume dataset is not only organized into one single bounding box, but into a hierarchy of bounding boxes like a uniform grid or an octree (cf. e. g. Section 16.5 from [SSC02]). Such hierarchies are used to implement acceleration techniques like empty-space skipping [LMK03].

### 3.2.2 Frequency Domain Volume Rendering

Frequency Domain Volume Rendering [TL93] (FDVR) works by applying a discrete Fourier transform to the volume dataset and exploiting the fact that in the frequency domain, according to the *Fourier slice-theorem*, the volume dataset can be reconstructed using a *single slice*. This effectively reduces the complexity of volume reconstruction from  $O(n^3)$  in terms of the participating voxels to  $O(n^2 \log n)$  time. Although extensions and even ports to GPUs were proposed [VKG04] [JvRLHK04], the major shortcomings of this technique remain